VLSI implementation of optimized 8-bit Brent-Kung parallel prefix adders in 45nm CMOS technology.

Stavros Spyridopoulos (stavspirid@gmail.com)

Quinten Kustermans (quinten.kustermans@home.nl)

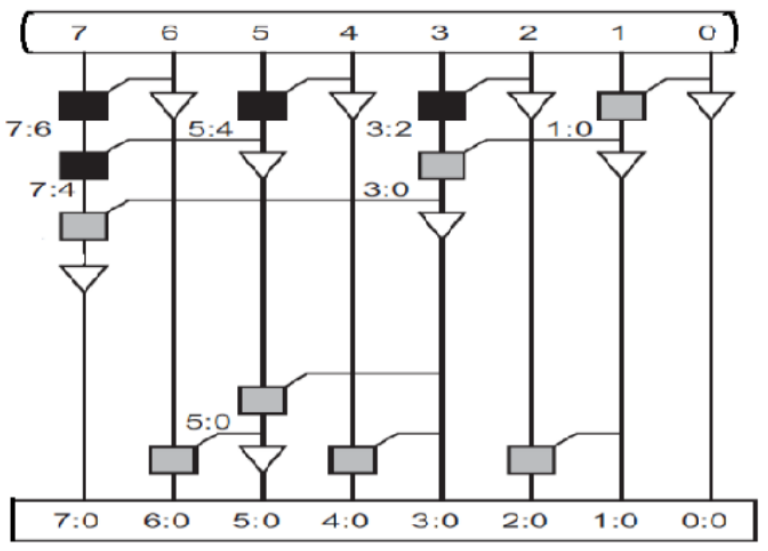

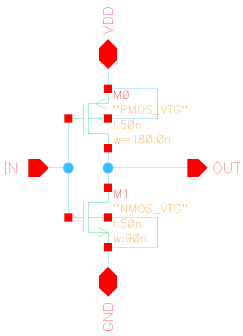

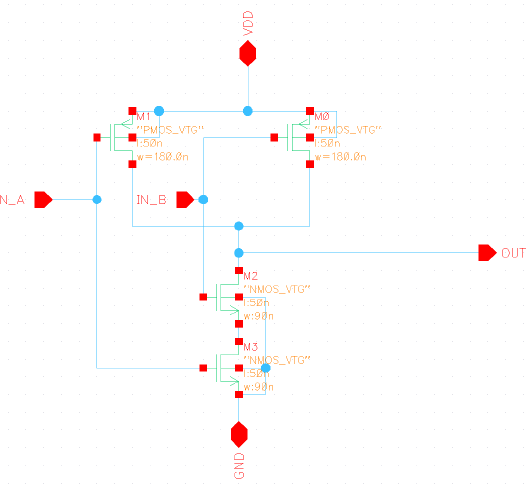

| Gate | Schematic | Transistors |

|---|---|---|

| Inverter |  |

2 |

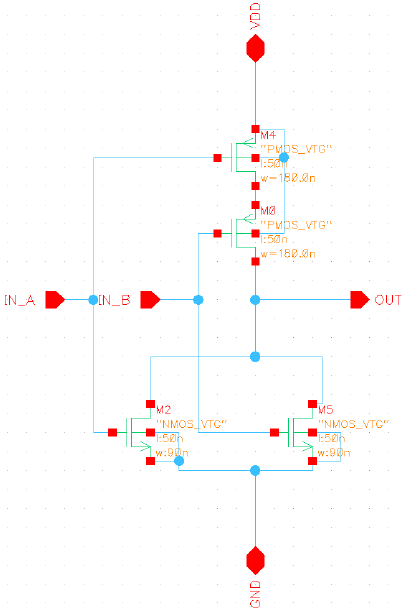

| NOR |  |

4 |

| NAND |  |

4 |

NMOS: 90nm width | PMOS: 180nm width (2:1 ratio for balanced timing)

Selected implementation: (A + B) + (A ∗ B) using 3 gates (2×NOR, 1×AND)

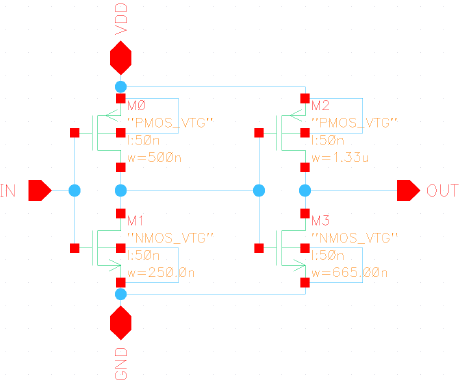

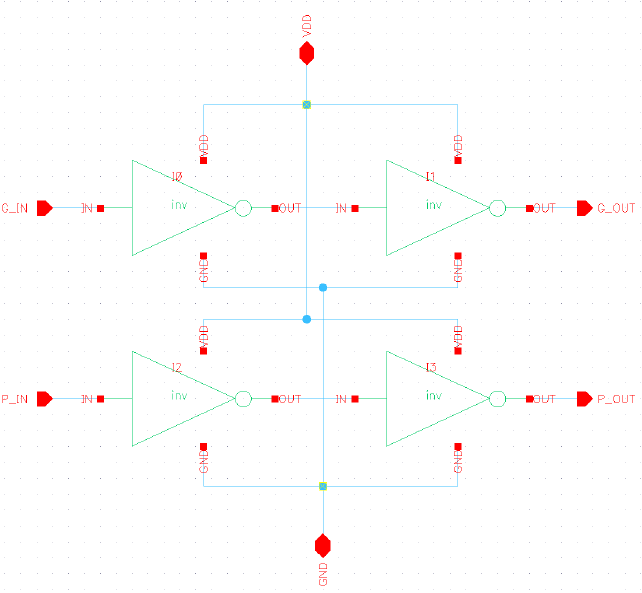

| Cell | Schematic | Transistors |

|---|---|---|

| Buffer |  |

8 |

| Black |  |

18 |

| Gray |  |

12 |

Compound gate technique reduces transistor count:

- Buffer: 4 transistors (50% reduction)

- Black: 14 transistors (22% reduction)

- Gray: 10 transistors (17% reduction)

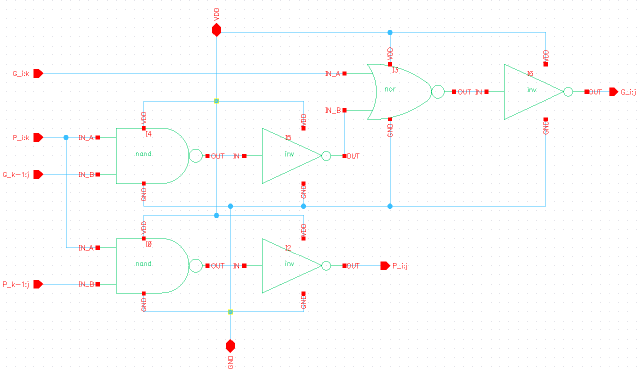

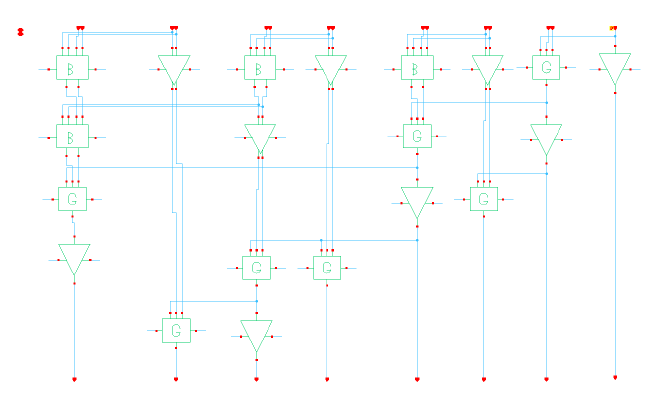

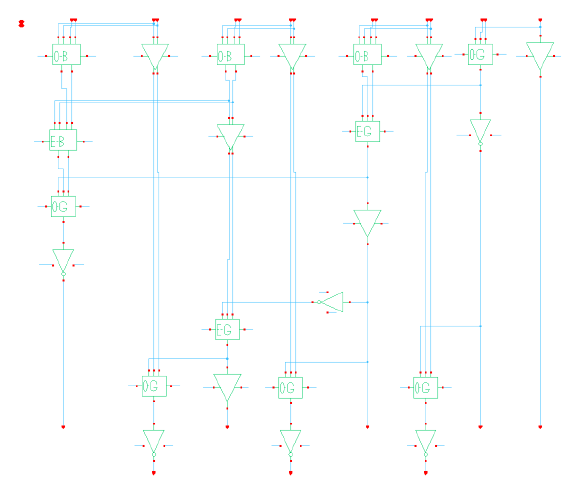

| Version | Schematic | Transistors | Area (μm²) |

|---|---|---|---|

| Unoptimized |  |

228 | 130.87 |

| Optimized |  |

160 | 109.13 |

Improvement: 30% fewer transistors, 16.6% smaller area

2-stage inverter chains improve timing:

- Rise time: 1115ps → 84ps

- Fall time: 743ps → 97ps

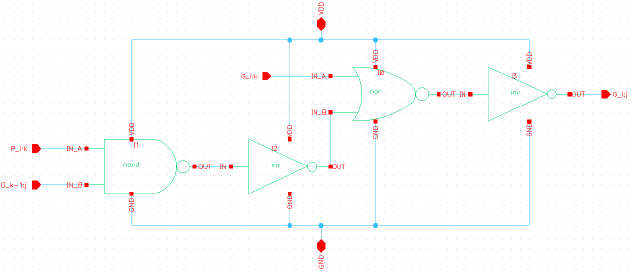

| NAND | NOR |

|---|---|

|

|

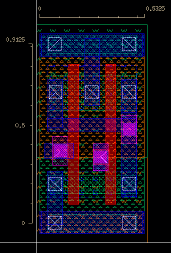

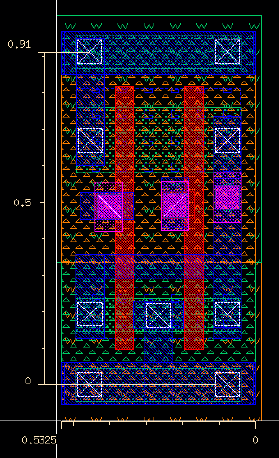

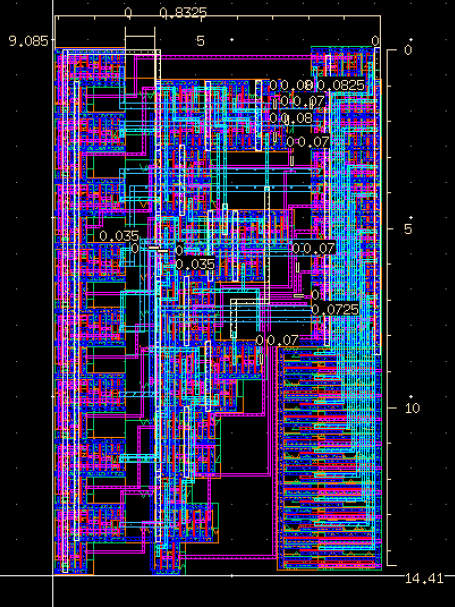

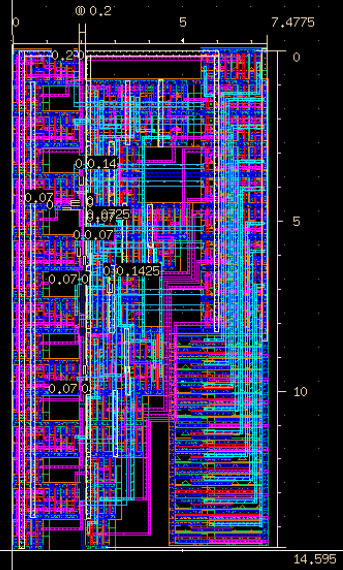

| Unoptimized (14.41×9.09 μm) | Optimized (14.60×7.48 μm) |

|---|---|

|

|

Layout Strategy: Lane-based design with hierarchical metal layers (M1-M5)

| Metric | Unoptimized | Optimized | Improvement |

|---|---|---|---|

| Delay | 1.065ns | 1.044ns | 2.0% |

| Power | 136.4μW | 140.1μW | -2.7% |

| Area | 130.87μm² | 109.13μm² | 16.6% |